CMOS射频集成电路设计 技术挑战、研发流程与未来展望

在当今无线通信技术飞速发展的时代,CMOS射频集成电路设计已成为推动移动设备、物联网和5G/6G通信等领域进步的核心驱动力。作为半导体行业的重要分支,它将传统的CMOS工艺与高频射频功能相结合,实现了高性能、低成本和高度集成化的解决方案。本文将深入探讨CMOS射频集成电路设计的技术挑战、研发流程及未来发展趋势。

一、CMOS射频集成电路设计的技术挑战

CMOS工艺最初是为数字电路优化的,其应用于射频领域面临诸多独特挑战:

- 高频性能限制:CMOS晶体管的截止频率和最大振荡频率虽已大幅提升,但在毫米波等极高频率下,其增益、噪声和线性度仍逊于GaAs或SiGe等工艺。

- 噪声与线性度权衡:射频前端需要低噪声放大器来接收微弱信号,同时要求功率放大器具备高线性度以避免失真。在CMOS中平衡这两者是一大难题。

- 集成干扰问题:将敏感的射频模块与数字基带、电源管理电路集成在同一芯片上时,衬底耦合、电源噪声和电磁干扰会显著影响性能。

- 无源元件优化:电感、变压器和电容等无源元件在CMOS中占用面积大、品质因数低,需通过三维结构或新材料来改进。

二、CMOS射频集成电路的研发流程

成功的CMOS射频IC研发遵循系统化流程:

- 系统架构设计:根据应用需求(如Wi-Fi、蓝牙或蜂窝通信),确定射频前端的整体架构,包括收发链路预算、调制方式和工艺节点选择。

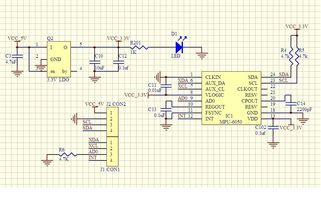

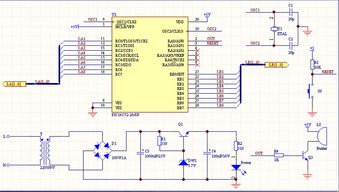

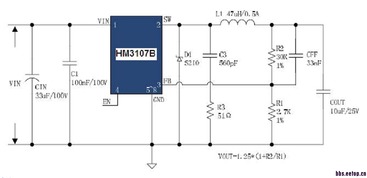

- 电路设计与仿真:使用EDA工具(如Cadence Virtuoso)进行晶体管级设计,重点优化低噪声放大器、混频器、压控振荡器和功率放大器等关键模块。仿真需涵盖直流、交流、瞬态和电磁分析。

- 版图设计与验证:射频版图需特别关注寄生效应、阻抗匹配和屏蔽措施。通过DRC和LVS确保制造可行性,并进行后仿真以评估实际性能。

- 流片与测试:在晶圆厂完成制造后,使用探针台和网络分析仪等设备测试芯片的S参数、噪声系数和输出功率,并与设计目标对比。

- 系统集成与优化:将射频IC嵌入PCB或封装模块中,进行整机测试,并迭代改进以解决实际应用中的问题。

三、未来发展趋势与创新方向

随着5G普及和6G研发启动,CMOS射频集成电路设计正迎来新的机遇:

- 毫米波与太赫兹技术:利用CMOS工艺的成本优势,开发工作在30GHz以上频段的芯片,支持高速数据传输和雷达传感。

- 异构集成:通过硅光电子、MEMS或先进封装技术,将CMOS与其他材料芯片集成,突破单一工艺的性能瓶颈。

- 智能化与可重构设计:引入AI算法优化电路参数,开发可软件定义的射频前端,以适应多频段、多模式通信需求。

- 能效提升:针对物联网设备,研发超低功耗射频IC,延长电池寿命并支持能量收集技术。

结论

CMOS射频集成电路设计是连接数字世界与无线信号的关键桥梁。尽管面临高频损耗、噪声干扰等挑战,但通过持续的材料创新、工艺进步和设计方法优化,它正不断拓展应用边界。从智能手机到自动驾驶,从智慧城市到太空通信,CMOS射频IC的研发将继续推动技术革命,塑造一个更加互联的未来。研发人员需跨学科协作,结合电路理论、半导体物理和系统思维,方能在这个充满活力的领域取得突破。

如若转载,请注明出处:http://www.laike-cloud.com/product/58.html

更新时间:2026-04-18 10:33:48