集成电路CAD设计中的核心环节 芯片焊盘与版图布局研发探析

在当今高速发展的半导体产业中,集成电路(IC)的计算机辅助设计(CAD)扮演着至关重要的角色。其中,芯片焊盘(Pad)设计与版图(Layout)布局设计不仅是连接芯片内部电路与外部世界的物理桥梁,更是决定芯片性能、可靠性及制造成本的关键研发环节。本文旨在深入探讨这两大核心设计领域的研发要点与技术趋势。

芯片焊盘设计:性能与可靠性的门户

芯片焊盘,作为芯片与封装基板或直接与印制电路板(PCB)进行电气连接和机械固定的金属区域,其设计直接影响到信号的完整性、电源的稳定性以及芯片的长期可靠性。

1. 设计考量与挑战:

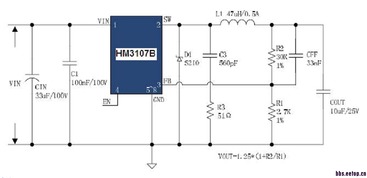

- 电气特性:焊盘的尺寸、形状和间距需精确计算,以匹配传输线的阻抗,减少信号反射与损耗,尤其是在高频、高速应用中。电源和接地焊盘需要足够大的面积和低阻抗路径,以确保稳定的电压供应和有效的噪声泄放。

- 机械与热可靠性:焊盘必须能够承受封装过程中的键合(如引线键合、倒装芯片凸点)应力,以及产品生命周期中的热循环应力。材料选择、焊盘下方的金属堆叠结构(Under Bump Metallization, UBM)设计都至关重要。

- 可制造性设计(DFM):设计需严格遵循晶圆厂和封装厂的设计规则(Design Rule),确保光刻、刻蚀、电镀等工艺的可行性,避免短路、断路等缺陷。

2. 研发趋势:

- 随着芯片向多芯片模块(MCM)、系统级封装(SiP)和2.5D/3D集成发展,焊盘设计变得更加复杂,需要支持更细间距的微凸点(Micro-bump)和硅通孔(TSV)技术。

- 针对先进工艺节点(如7nm、5nm及以下),焊盘设计需与前端设计(FEOL)协同优化,以应对更严格的电迁移(Electromigration)和自热效应挑战。

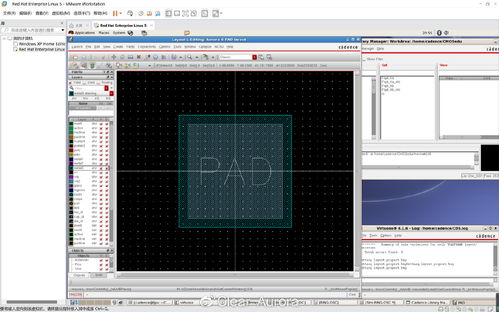

版图布局设计:性能、功耗与面积的精妙平衡

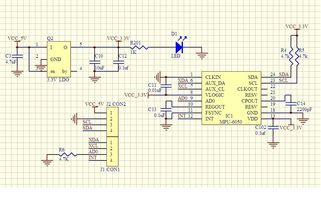

版图布局是将电路网表(Netlist)转化为一系列几何图形(多边形)的过程,这些图形定义了芯片上每一层材料的形状,是集成电路物理实现的蓝图。

1. 设计核心任务:

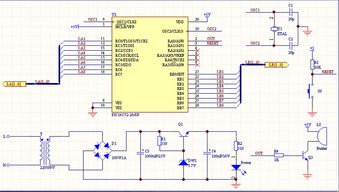

- 物理实现:根据逻辑综合后的网表,进行布局(Placement)、布线(Routing)和物理验证(Physical Verification)。布局决定了每个标准单元、宏模块(如存储器、模拟模块)在芯片上的位置,目标是优化时序、降低互连线延迟和功耗。

- 信号完整性管理:在高密度设计中,串扰(Crosstalk)、电源网络噪声(IR Drop、电源地反弹)等问题突出。研发重点在于通过合理的电源网格设计、时钟树综合(CTS)和屏蔽布线等技术来保障信号纯净度。

- 设计规则与工艺兼容性:必须严格遵守复杂的几何设计规则(DRC)、电气规则(ERC)以及针对可制造性的规则(如光学邻近效应修正OPC、多重图形化要求)。

2. 研发方法与工具演进:

- 自动化与智能化:传统的全定制(Full-custom)和半定制(Semi-custom)设计方法正与高度自动化的数字设计流程(RTL-to-GDSII)深度融合。机器学习(ML)和人工智能(AI)技术开始应用于布局预测、热点检测和设计空间探索,以加速迭代并优化PPA(性能、功耗、面积)。

- 系统级协同设计:版图设计不再孤立,需要与系统架构、封装设计(Co-design)乃至散热分析进行早期协同。对于模拟/射频电路和高速数字接口,版图的物理效应(寄生参数)必须在前端设计阶段就被充分考虑。

- 应对先进工艺:在FinFET、GAA等晶体管结构下,版图设计需处理三维效应、更复杂的器件模型和更苛刻的可靠性约束(如自热、NBTI等)。

面向未来的研发融合

芯片焊盘设计与版图布局设计是集成电路CAD研发中密不可分的两部分。焊盘是芯片对外的“接口标准”,而版图则是其内部的“城市规划和交通网络”。未来的研发方向将更加注重:

- 前后端与封装的协同优化:从系统级出发,实现芯片-封装-板级的统一设计和优化。

- EDA工具的持续创新:开发更智能、更高效的CAD工具,以管理日益增长的设计复杂度和数据量。

- 新材料与新工艺的快速适配:针对碳纳米管、二维材料等新兴半导体技术,以及新型封装形式,迅速建立相应的设计方法和规则。

在摩尔定律持续推进与超越摩尔定律(More than Moore)并行的时代,对芯片焊盘及版图布局设计的深入研发,是保障我国集成电路产业自主创新与核心竞争力提升的关键技术基石。工程师们需要在严谨的物理约束与创造性的设计优化之间不断探索,方能铸造出性能卓越、稳定可靠的芯片产品。

如若转载,请注明出处:http://www.laike-cloud.com/product/57.html

更新时间:2026-04-18 08:13:54