数字集成电路的分类与特点解析 从设计到研发的视角

数字集成电路是构成现代信息社会的基石,从智能手机到数据中心,其身影无处不在。其研发过程高度复杂且分工明确,而不同类型的数字电路在设计与应用上各有千秋。本文将从研发的视角,系统解析数字集成电路的主要分类及其核心特点。

一、 按集成度分类:规模决定复杂度

这是最基础、最直观的分类方式,直接反映了芯片的工艺水平和设计能力。

- 小规模集成电路(SSI):包含逻辑门数量通常在10个以下,如基本的与门、或门、非门等。

- 特点:结构简单,功能单一,常用于教学、原型验证或作为更大系统中的基础构件。

- 研发侧重:在先进工艺节点下,单独研发SSI已不常见,其设计更多作为标准单元库的一部分,由晶圆厂或IP公司提供。

- 中规模集成电路(MSI):包含逻辑门数量在10至100个之间,如编码器、译码器、计数器、寄存器等。

- 特点:实现了特定的逻辑功能模块,是构建复杂系统的“积木块”。

- 研发侧重:通常作为标准IP(知识产权核)进行设计和验证,强调功能的正确性、时序的稳定性和接口的标准化,以便在不同项目中复用。

- 大规模集成电路(LSI):包含逻辑门数量在100至10,000个之间,如早期的微处理器、存储器芯片、简单微控制器等。

- 特点:可完成一个子系统或一个完整的功能,如8位CPU。

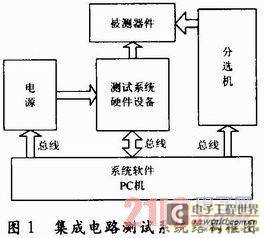

- 研发侧重:开始涉及系统架构设计、模块划分、片上总线设计等。研发流程需要完整的数字前端(RTL设计、验证)和后端(物理设计)团队协作。

- 超大规模集成电路(VLSI):包含逻辑门数量在10,000至1,000,000个之间,是现代芯片的主流,如复杂的微处理器、DSP、SoC中的主要模块。

- 特点:集成度极高,性能强大,设计复杂。

- 研发侧重:高度依赖电子设计自动化(EDA)工具。研发核心挑战包括时序收敛、功耗管理(动态与静态)、信号完整性、可测试性设计(DFT)以及巨大的验证工作量。团队需要精通特定领域(如CPU、GPU、AI加速器)的架构师。

- 特大规模集成电路(ULSI)和巨大规模集成电路(GSI):门数量超过百万甚至数十亿,代表最先进的工艺水平,如多核CPU、高端GPU、大型SoC。

- 特点:采用纳米级工艺,集成了处理器、存储器、接口、模拟模块等,形成一个完整的片上系统。

- 研发侧重:研发是一项庞大的系统工程。特点包括:

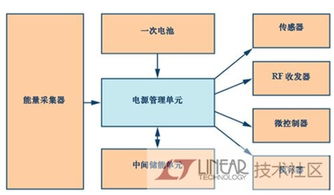

- 异构集成:整合不同架构的计算单元(CPU/GPU/NPU)。

- 软硬件协同设计:芯片设计与系统软件、驱动、编译器同步进行。

- 先进封装:可能采用2.5D/3D封装技术以继续提升性能、降低功耗。

- 高昂的成本与风险:研发投入动辄数亿美元,对团队技术、管理和资金都是极限考验。

二、 按电路结构分类:架构决定应用

此分类决定了芯片的执行模式和工作原理。

- 通用型集成电路:

- 代表:微处理器(MPU)、微控制器(MCU)、数字信号处理器(DSP)。

- 特点:通过执行存储的程序(软件)来完成多样化的任务,灵活性极高。

- 研发特点:研发聚焦于提升核心的通用计算性能(IPC、主频)、能效比、指令集扩展(如向量、AI指令),以及构建丰富的外设生态。

- 专用集成电路:

- 代表:专用标准产品(ASSP),如手机基带芯片、音视频编解码芯片。

- 特点:为特定应用或市场设计,功能固定,在特定任务上性能和能效通常优于通用芯片。

- 研发特点:深度定制化设计,算法硬件化是关键。研发团队需与算法团队紧密合作,进行硬件/软件划分,用专用硬件电路(如流水线、并行处理单元)实现关键算法,以追求极致的吞吐量和能效。

- 可编程逻辑器件:

- 代表:现场可编程门阵列(FPGA)、复杂可编程逻辑器件(CPLD)。

- 特点:硬件功能可由用户通过编程(烧写配置文件)来定义,提供了硬件灵活性与高性能的折中方案。

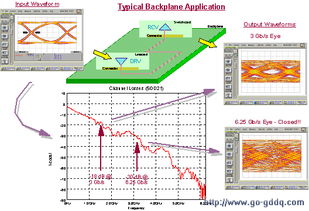

- 研发特点(指FPGA芯片本身的研发):研发重点在于设计可编程的布线资源、逻辑单元(CLB)、嵌入式硬核(如SerDes、DDR控制器)和丰富的IP库。其挑战在于如何在提供灵活性的尽量减少由此带来的面积、功耗和速度上的开销。

三、 按制造工艺分类:工艺奠定基石

工艺是芯片物理实现的载体,直接影响性能、功耗和成本。

- CMOS工艺:当今绝对的主流。

- 特点:静态功耗极低(仅漏电功耗),集成度高,抗干扰能力强,已成为数字IC的标准工艺。

- 研发影响:几乎所有数字芯片研发都基于CMOS工艺库。研发人员必须深刻理解工艺节点(如7nm、5nm)带来的物理效应(短沟道效应、迁移率变化等),并利用工艺提供的特殊器件(如FinFET)进行设计。

- 双极型工艺(如TTL、ECL):曾经的主流,现多用于特殊领域。

- 特点:速度快,驱动能力强,但功耗大,集成度低。

- 研发影响:在现代超高速(如微波、光纤通信)或高驱动需求的部分模拟/混合信号电路中仍有应用。相关研发需要专业的模拟/射频设计知识。

研发视角下的:

数字集成电路的分类并非孤立,而是交织在一起,共同定义了一款芯片的“身份”。在研发实践中,选择何种类型的芯片进行开发,取决于目标市场、性能需求、功耗预算、研发周期和成本约束。例如,研发一款AIoT设备的主控芯片,可能选择基于成熟CMOS工艺,集成一个MCU核心、专用AI加速模块和多种接口的SoC(属于VLSI/ULSI范畴的ASSP)。整个过程需要系统架构师、数字设计工程师、验证工程师、物理设计工程师和软件工程师的紧密协作,穿越从行为级描述到GDSII版图的完整研发流程,最终将抽象的算法和逻辑,转化为实实在在的硅芯片。理解这些分类与特点,是成功进行数字IC研发的第一步。

如若转载,请注明出处:http://www.laike-cloud.com/product/79.html

更新时间:2026-04-20 10:55:18