通信集成电路芯片物理设计中的核心挑战与创新解决方案

随着5G、卫星通信、高速以太网等技术的飞速发展,通信集成电路芯片正朝着更高频率、更高带宽、更低功耗和更大规模集成的方向演进。这给芯片的物理设计(Physical Design)环节带来了前所未有的复杂性和一系列技术难点。物理设计是将电路逻辑网表转化为可供制造的物理版图的桥梁,其质量直接决定了芯片的最终性能、功耗、面积和可靠性。本文将深入剖析通信芯片物理设计中的主要难点,并探讨相应的解决方案与研发趋势。

一、 通信芯片物理设计的主要难点

- 高频高速信号的完整性:通信芯片的核心在于信号的收发与处理。工作频率从数GHz到数十GHz,甚至向太赫兹迈进,带来了严重的信号完整性问题,包括:

- 时序收敛困难:高频下时钟抖动、时钟偏差(Skew)对建立/保持时间的影响被放大,时序路径的余量极小,收敛极其困难。

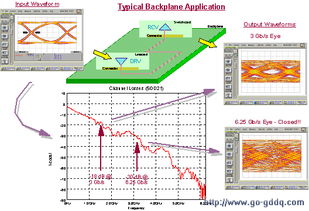

- 串扰与噪声:密集布线中相邻信号线之间的电容、电感耦合会导致信号串扰,破坏信号波形,引起误码。电源/地网络的噪声(IR Drop、地弹)也会严重影响高速模拟/射频模块和敏感数字电路的性能。

- 传输线效应:当信号波长与互连线长度可比拟时,互连线不再是理想导体,而需作为传输线处理,阻抗匹配、反射、损耗成为必须精细控制的问题。

- 混合信号与射频集成:现代通信芯片多为数模混合SoC,在同一颗芯片上集成了高性能的射频前端、高速数据转换器(ADC/DAC)、模拟锁相环(PLL)以及大规模数字基带处理器。难点在于:

- 噪声隔离:数字电路的开关噪声(通过衬底和电源网络)极易干扰敏感的模拟和射频电路,导致性能恶化(如相位噪声增加、信噪比下降)。

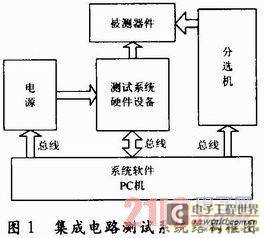

- 版图布局的协同优化:模拟/射频部分的版图需要手工精心设计,讲究对称性、匹配性和寄生控制,而数字部分采用自动布局布线(APR),两者在布局规划、电源网络、隔离结构上需要深度融合与协同设计。

- 功耗与热管理的严峻挑战:为支持高速数据处理和传输,芯片功耗急剧上升。功耗难点体现在:

- 动态功耗与静态功耗:高频开关活动导致动态功耗巨大;采用先进工艺节点(如7nm、5nm)后,静态漏电功耗占比显著提升。

- 局部热点:功率放大器(PA)、高速SerDes等模块功耗密度极高,易形成局部热点,影响器件寿命和电路可靠性,并可能引发热致电迁移故障。

- 电源完整性:巨大的瞬态电流导致电源网络出现显著的IR Drop,使得晶体管实际驱动电压不足,性能下降,严重时导致功能失效。

- 先进工艺节点的复杂性:为追求更高性能和集成度,通信芯片普遍采用16nm及以下的先进工艺,这引入了新的物理效应:

- 制造变异性与良率:光刻、化学机械抛光等工艺步骤的微小变异对器件和互连线特性的影响(如线边缘粗糙度、厚度变化)更为显著,直接影响电路性能和成品率。

- 设计规则激增:双重 patterning/四重 patterning、FinFET器件结构等使得物理验证(DRC/LVS)规则极其复杂,版图设计约束增多。

- 寄生参数提取与建模:三维互连结构复杂,寄生电阻、电容、电感(RLCK)的精确提取和建模至关重要,但计算量巨大且准确性要求极高。

二、 针对难点的解决方案与研发方向

- 面向信号完整性的设计流程与工具:

- 签核驱动的设计流程:在设计早期(如布局阶段)就引入基于签核精度的分析(如静态时序分析STA、电源完整性分析),进行预测和优化,而非仅在最后阶段验证。

- 协同设计与分析:将电磁场仿真、传输线分析、电源噪声分析与传统的布局布线工具深度集成,实现布线前、布线中、布线后的实时评估与优化。例如,采用屏蔽线、差分对布线、自动阻抗控制布线等技术。

- 先进的时序收敛方法:运用片上偏差(OCV)高级建模、时钟树综合(CTS)与时钟网格(Clock Mesh)混合结构、有用的时钟偏差(Useful Skew)等技术来应对高频时序挑战。

- 混合信号隔离与协同设计技术:

- 物理隔离策略:采用深N阱(DNW)、保护环(Guard Ring)、隔离沟槽、独立电源域和地平面,从物理上阻断噪声耦合路径。

- 规划驱动的混合信号布局:在顶层规划阶段就为模拟/射频模块划分专属区域,预留足够的隔离空间,并规划全局的电源分配网络(PDN),确保数字和模拟电源/地分离且低噪声。

- 统一的设计环境:研发支持数字、模拟、射频统一数据模型和设计流程的EDA平台,实现跨域约束传递和联合仿真。

- 多维度功耗与热完整性优化:

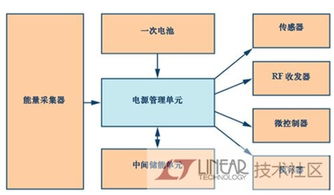

- 系统级与架构级低功耗设计:采用动态电压频率缩放(DVFS)、电源门控(Power Gating)、多阈值电压(Multi-Vt)库、时钟门控(Clock Gating)等技术。

- 精细化电源网络设计与分析:使用高密度去耦电容(Decap)、片上稳压器、网格状电源地网络,并运用基于机器学习的IR Drop热点预测工具进行早期优化。

- 热感知布局与封装协同设计:在布局时考虑功耗分布,将高功耗模块分散或靠近散热通道;采用先进封装技术(如硅中介层、3D IC)增强散热能力,并进行芯片-封装-系统(CPS)级热仿真。

- 应对先进工艺的设计方法学创新:

- 设计-工艺协同优化(DTCO):在设计阶段就考虑工艺限制和变异,通过版图风格(Layout Style)优化、使用标准单元增强技术(如采用多高度单元、利用布线资源)来提升性能和良率。

- 机器学习辅助设计:利用机器学习模型预测布线拥塞、时序、功耗和良率,加速设计空间探索,自动优化布局布线策略,甚至自动生成部分模拟模块的版图。

- 高精度物理验证与仿真:采用基于场求解器的3D寄生参数提取工具,以及能够处理复杂设计规则的增量式物理验证引擎,确保设计的可制造性。

三、 结论

通信集成电路芯片的物理设计是一项涉及电路、器件、工艺、封装、EDA工具等多学科的复杂系统工程。其核心难点围绕着高频、混合信号、低功耗和先进工艺四大主题展开。解决这些难题没有单一的“银弹”,而需要一整套从设计方法学、EDA工具链到跨领域协同创新的综合解决方案。随着6G、太赫兹通信等前沿技术的发展,物理设计将面临更极端的频率、更异构的集成和更严苛的能效要求。研发的重点将继续向更智能(AI/ML驱动)、更协同(芯片-封装-系统一体化)、更精准(量子级效应建模)的方向演进,以支撑下一代通信系统的芯片实现。

如若转载,请注明出处:http://www.laike-cloud.com/product/73.html

更新时间:2026-04-12 17:16:56