合创资本刘华瑞 聚焦数字集成电路设计领域的研发趋势与投资逻辑

在半导体产业中,数字集成电路(Digital IC)作为信息处理与计算的核心,其设计研发的前沿动态与创新方向,一直是产业界与投资界关注的焦点。合创资本合伙人刘华瑞先生,凭借其深厚的产业背景与敏锐的投资洞察,对数字IC设计领域的研发趋势有着独到的见解。本文将结合刘华瑞的观点,探讨当前数字集成电路设计领域的关键研发关注点。

一、高性能计算与异构集成的核心驱动力

刘华瑞指出,随着人工智能、大数据、云计算等应用的爆发式增长,市场对算力的需求呈指数级攀升。这直接驱动了数字IC设计向更高性能、更低功耗的方向演进。传统的同构计算架构已逐渐遇到瓶颈,因此,异构计算与集成成为研发的核心路径。这不仅仅是CPU、GPU、FPGA、ASIC等不同计算单元在系统级的组合,更深入到芯片级(Chiplet)甚至IP核级别的紧密集成与协同。研发重点在于如何通过先进的架构设计、互联协议(如UCIe)、封装技术(如2.5D/3D封装)和软件工具链,实现异构单元间的高效、低延迟、高带宽通信与任务调度,从而最大化整体能效比。

二、先进工艺节点下的设计挑战与协同优化

工艺制程的持续微缩(如向3nm、2nm及以下演进)在带来性能提升和功耗降低的也引入了前所未有的设计挑战。刘华瑞强调,研发的关注点已从单纯追求工艺领先,转向 “设计-工艺协同优化”(DTCO) 和 “系统-技术协同优化”(STCO) 。这要求设计团队必须深入理解物理效应(如寄生效应、量子隧穿、工艺波动)、制造良率与可靠性问题,并在架构设计、电路设计、物理实现乃至EDA工具流程的各个环节进行精细化权衡与创新。例如,在标准单元库设计、时钟网络架构、电源完整性、信号完整性以及热管理等方面,都需要全新的设计方法论和工具支持。

三、从专用到可重构:灵活性与效率的平衡

面对快速变化的市场需求和应用场景的多样化,刘华瑞观察到,数字IC的研发正寻求在专用化(针对特定算法或任务进行极致优化,如AI加速器、DPU)与灵活性之间找到最佳平衡点。因此,可重构计算架构成为重要研发方向。这类架构(如某些先进的FPGA、CGRA可重构阵列)能够在硬件层面根据不同的计算任务进行动态配置,兼具ASIC的高能效和通用处理器的灵活性。其研发难点在于如何设计高效的可重构单元、互连网络以及配套的编译工具,以降低开发门槛并充分发挥硬件潜力。

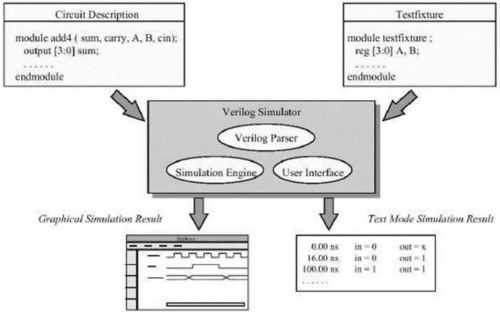

四、全流程EDA工具与设计方法学的创新

数字IC设计的高度复杂性使得EDA工具和设计方法学成为研发不可或缺的基石。刘华瑞认为,随着系统复杂度和异构性的增加,传统的设计流程正在被重塑。研发的关注点包括:

- 高层次综合(HLS)与敏捷验证:将设计抽象层次从RTL进一步提升,使用C/C++/SystemC等进行功能描述和快速原型验证,以加速设计迭代。

- AI驱动的EDA工具:利用机器学习技术优化布局布线、时序收敛、功耗分析等环节,提升设计自动化水平和结果质量。

- 系统级设计与验证平台:构建包含硬件、软件、甚至应用场景的虚拟原型,实现更早期的软硬件协同设计与性能评估。

五、安全与可靠性的底层基石地位

在万物互联的时代,芯片的安全性(Security)和功能安全性(Functional Safety)已从附加属性转变为必备属性。刘华瑞特别强调,在数字IC的研发初期就必须将安全架构纳入核心考量。这涉及硬件安全模块(如PUF、真随机数发生器、加密引擎)、侧信道攻击防护、安全启动、信任根建立以及面向汽车、工业等领域的高可靠性设计(如遵循ISO 26262、IEC 61508等标准)。这方面的研发需要从系统架构到电路实现的全面加固。

刘华瑞的观点揭示,数字集成电路设计的研发前沿是一个多维度、多层次协同演进的生态系统。它不仅是晶体管与电路的创新,更是架构、算法、软件、工艺、封装乃至安全理念的深度融合。对于投资者和创业者而言,理解这些深层次的研发趋势,把握其中在异构集成、设计方法学、能效平衡以及系统级安全等方面涌现出的创新机会,是在数字IC设计这一高技术壁垒、高价值赛道中取得成功的关键。未来的领先芯片,必将是那些在性能、能效、灵活性和可靠性上取得卓越平衡的系统级创新成果。

如若转载,请注明出处:http://www.laike-cloud.com/product/40.html

更新时间:2026-04-16 12:25:29